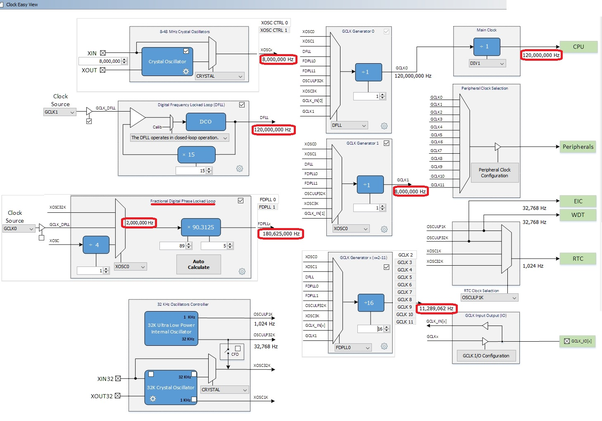

数字锁相环采用快速傅里叶变换(FFT)对下行载波信号进行快速频谱分析,可直接将VCO的频率引导到下行载波频率上;同时实现了载波跟踪与多普勒频率测量功能。通常用于产生更高的时钟频率,例如用于主系统时钟的时钟频率。 FDPLL的另一种类型是分数数字锁相环,可用于生成特定外围设备(例如I2S)所需的精确频率,如I2S音频编解码器。 这里是一个用于配置时钟在ATSAME54P20A微控制器的时钟对话框GUI,下图是ARM Cortex-M4部分:

8 MHz晶体振荡器信号显示为XOSC0(8,000,000 Hz)。它通过时钟发生器1(GCLK1)馈入数字锁频环,该时钟发生器将频率提高到120,000,000 Hz(120 MHz),这是由右上角的主时钟(CPU)使用的。 同时,还将8 MHz XOSC0信号反馈到FDPLL,并生成2 MHz信号(因为此FDPLL仅接受32 kHz至3.2 MHz之间的输入)。然后,它使用乘法器和除法器的组合,以产生180,625,000 Hz的输出。 那么为什么是那个频率?因为我想为以44.1 kHz的采样频率(与CD使用的采样频率相同)运行音频编解码器,以便生成MCLK(主时钟)。MCLK为256 x FS或256 x 44,100 = 11,289,600 Hz,44,100是采样率或帧同步(FS)。将其乘以16,将获得180,633,600 Hz。FDPLL最接近的频率为180,625,000 Hz,即降低了0.005%。 在底部的时钟生成器2中被16分频后,FS达到11,289,062 Hz,采样率达到44,097.9 Hz。 总的来说,这部分有12个通用时钟发生器模块(GCLK0、1和2-11),每个模块都有一个多路复用器,可以从8个或9个源中反馈输入信号,并可以分频为1到255。然后可以将它们按路线发送到各种外设(定时器,ADC,I2C,i2S,SPI,UART,USB等)或输出引脚中。

理工酷

理工酷

资源下载

资源下载